HDMI一致性测试中的3.3V上拉配置详解

本次主题聚焦于HDMI一致性测试中关键的3.3V上拉设置。专业工程师皆知,在进行HDMI一致性测试时,无论是单端还是差分信号测试,均需对TMDS信号(Clock+/−, Data0+/−, Data1+/−, Data2+/−)实施3.3V上拉。差分测试需4路上拉,而单端测试则需分别对正负信号上拉,共计8路。

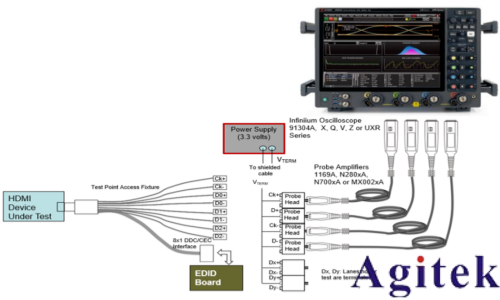

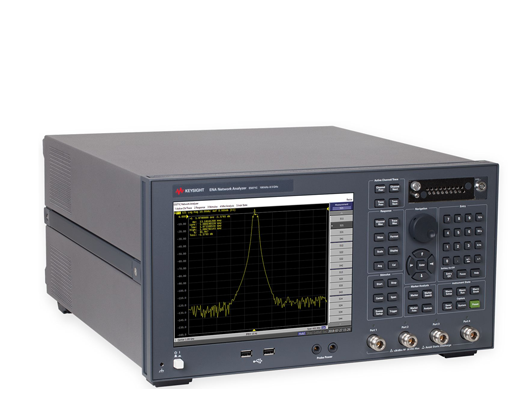

若使用Keysight较早的90000系列示波器,需搭配N5380A/B模块,并依赖外部3.3V电源完成上拉。受限于通道数量,仅能接入4支探头加N5380,因此在单端测试中,仅Clock及一Lane Data的4路信号可通过该模块上拉,其余两Lane的4路信号则需额外提供3.3V上拉。而使用90000X、UXR或MX0105A等新型示波器时,可直接在探头设置中配置3.3V偏置,简化操作,仅需关注未接入通道的上拉即可。实验室设备以Keysight为主,其他品牌较少,若使用其他示波器,建议联系厂商AE沟通实现方式,但测试原理均源自HDMI协会规范,本质一致。

以下从三方面深入解析:

一、为何需对另两Lane进行上拉?

HDMI 2.0 True 4K的眼图测试属于单端项目。接入示波器的Clock与Data必须上拉,否则TMDS信号无法输出,示波器亦无信号可采。同理,未接入的两Lane若不上拉,也无法激活信号。此时测试无法反映四通道同时工作的实际干扰情况。理论上,不上拉时测得的眼图会更“干净”,结果更优,但这不符合真实使用场景。反向思考,通过对比上拉与不上拉的状态,反而可量化通道间串扰影响,具备研究价值。

二、上拉与不上拉的实测对比

身边的硬件工程师实力出众,产品品质稳定。以下为实测眼图对比,唯一变量为未测试Data Lane是否上拉3.3V,其余条件完全一致。

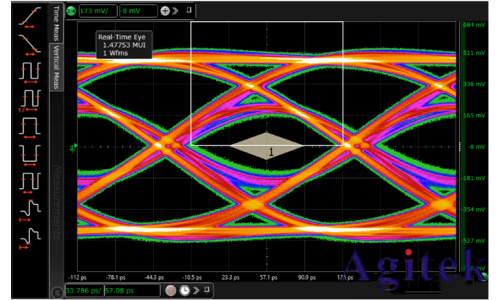

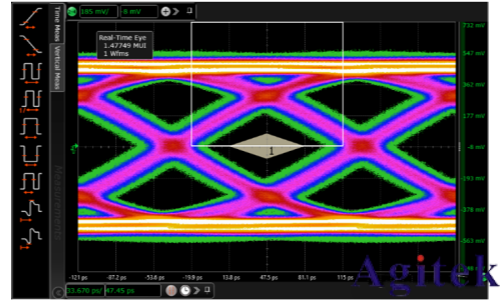

未上拉时眼图:信号干净,抖动小,看似“理想”。

上拉后眼图:因四通道同时工作,互扰显现,眼图略闭合,但更贴近真实工况。

结果与理论一致:当Clock与全部三对Data同时激活,系统干扰显著高于仅一对Data工作时。若仅作初步信号评估,趋势观察,可适当放宽要求;但作为专业测试工程师,每一份报告都应真实还原设计表现,细节不容妥协。

三、如何实现上拉?

进行HDMI标准接口一致性测试,多数采用Wilder的Fixture,部分具备能力的公司自研治具,但原理相近。推荐使用Wilder的Termination Module,集成8路上拉设计:4路供示波器接入信号使用,另4路专为未接入信号预留。外观精巧,性能可靠,售价1288美元,叠加运费、关税、增值税及清关费用后仍属合理投入。相较于示波器成本,此支出可控,值得配置。

理解原理后,自制方案亦不复杂:可利用USB 5V供电,经LDO稳压为3.3V(需确保输出质量),再分出4路或8路至SMA接口,测试时接入治具即可。若追求测试环境的专业性与行业认可度,选择Wilder等品牌仍是更稳妥的选择。

技术支持

关注官方微信

关注官方微信