什么是电容串扰?高速电子系统中的隐形干扰源

在当今技术飞速发展的时代,电子产品的设计正朝着高度集成化与高速化的方向迈进。随着器件尺寸不断缩小,数据传输速率却持续攀升至新的量级。这一趋势使得信号完整性(Signal Integrity, SI)问题日益凸显,其中传输线间的串扰(Crosstalk)现象已成为高速电路设计中最具挑战性的技术难题之一。

串扰的物理本质与电磁耦合机制

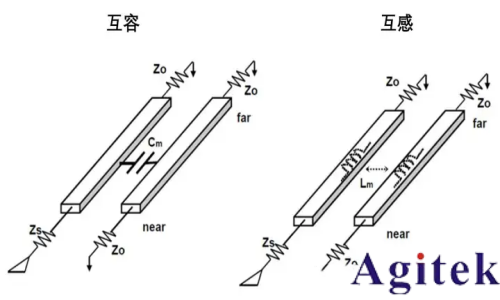

当高速信号在传输线中传播时,信号路径与其返回路径之间会形成动态的电磁场分布。这种延伸至导体周围的电磁场被称为边缘场(Fringing Field),其能量会通过互容(Mutual Capacitance)和互感(Mutual Inductance)两种耦合机制,以电磁耦合的形式转移到相邻的传输线上。这种能量转移现象即构成串扰的核心机制。

从电磁场理论视角分析,串扰本质上是传输线间通过电磁耦合实现的能量再分配过程。根据耦合路径的差异,串扰可分为容性耦合与感性耦合两种基本类型,二者在高速信号传输中往往同时存在并相互影响。

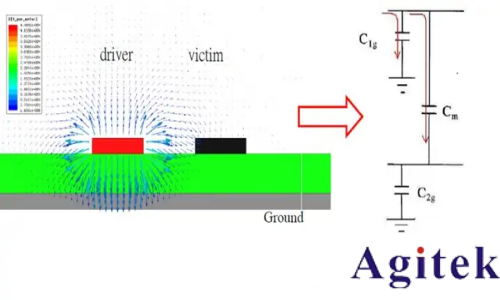

容性耦合:电场驱动的电压干扰

互容的物理定义

互容(Cₘ)是描述两个导体间通过电场耦合强度的物理量,其定义为:当驱动线与被扰线之间存在单位电压差时,两导体间积累的电荷量。数学表达式为:

Cm=VQ

其中Q为耦合电荷量,V为驱动线电压。

容性耦合机制

在时变信号作用下,驱动线的电压变化(dV/dt)会在互容Cₘ上产生位移电流,该电流通过被扰线的输入阻抗形成感应电压。这种电压耦合效应在数字电路中表现为:

信号跳变沿引发的瞬态干扰

近端串扰(NEXT)中的容性分量

高阻抗节点处的显著电压扰动

容性耦合强度与以下因素密切相关:

导体间距:间距减小导致Cₘ呈指数增长

介质常数:高介电常数材料增强电场耦合

平行走线长度:耦合能量随长度线性增加

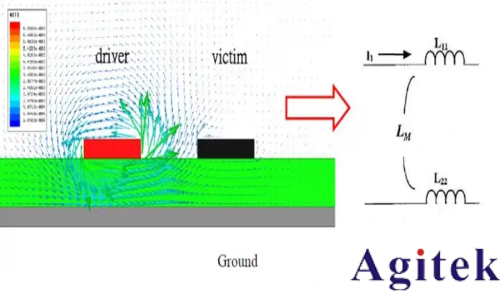

感性耦合:磁场诱导的电流干扰

互感的物理定义

互感(Lₘ)表征两个导体间通过磁场耦合的强度,其定义为:当驱动线中流过单位电流时,通过互感在被扰线中产生的磁通链数。数学表达式为:

Lm=IΨ

其中Ψ为磁通链,I为驱动线电流。

感性耦合机制

驱动线的时变电流(dI/dt)会产生变化的磁场,根据法拉第电磁感应定律,该磁场在被扰线中感应出电动势,进而形成干扰电流。这种电流耦合效应在数字电路中表现为:

信号跳变沿引发的瞬态电流

远端串扰(FEXT)中的感性分量

低阻抗回路中的显著电流扰动

感性耦合强度受以下因素影响:

回路面积:增大回路面积显著提升Lₘ

导体间距:间距减小导致磁场耦合增强

信号频率:高频信号使dI/dt效应加剧

串扰的时域与频域特性

在时域分析中,串扰表现为:

近端串扰(NEXT):干扰信号向信号源方向传播

远端串扰(FEXT):干扰信号向接收端方向传播

脉冲展宽效应:导致信号边沿速率下降

频域分析揭示:

串扰幅度随频率升高而增大

容性耦合在高频段占主导

感性耦合在中频段更显著

阻抗不连续点引发谐振增强

现代高速设计中的串扰控制策略

为有效抑制串扰,现代高速电路设计采用多维度控制技术:

空间隔离技术:

3W/5W布线规则(线间距≥3倍线宽)

差分对布线优化

防护走线(Guard Trace)应用

介质材料优化:

低介电常数(Dk)基板材料

嵌入式电容材料应用

均匀介质层设计

拓扑结构改进:

阻抗匹配网络设计

端接电阻优化配置

飞线(Fly-by)拓扑应用

先进封装技术:

硅通孔(TSV)三维集成

倒装芯片(Flip Chip)封装

嵌入式微带线结构

电容串扰作为高速电子系统中的固有物理现象,其影响随着信号速率的提升呈非线性增长。通过深入理解互容与互感的耦合机制,结合先进的电磁仿真工具与系统级设计方法,工程师能够在纳米级工艺节点下实现串扰的有效控制。未来,随着人工智能辅助设计与新材料技术的突破,串扰抑制技术将持续演进,为5G/6G通信、人工智能计算等前沿领域提供可靠的信号完整性保障。

技术支持

关注官方微信

关注官方微信