用于高速系统验证与一致性测试的全新去嵌入、嵌入与均衡软件

高速系统的验证与一致性测试

高速系统的验证与一致性测试需要对从DUT到示波器输入的完整信号路径具备可视性。这意味着要去嵌入测试夹具与互连,嵌入真实系统条件,并且在某些情况下应用接收端均衡以仿真Tx/Rx行为。只有这样,才能同时确认一致性与真实世界性能。

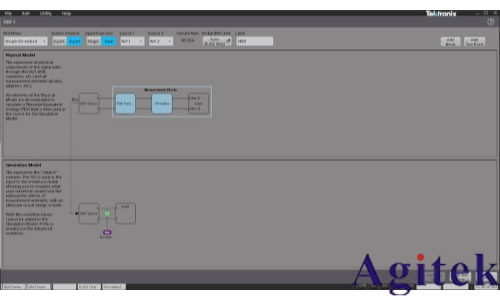

Tektronix全新的Signal Integrity Modeling(SIM)软件——适用于5 Series B MSO、6 Series B MSO与7 Series DPO示波器——让你可以直接在示波器上对信号进行去嵌入、嵌入与均衡。

从PCIe、DDR5、USB4与多通道以太网等多千兆串行设计,到前沿RF与电力电子,SIM都有助于确保你的设计满足一致性和真实世界性能要求。通过去除并仿真来自电缆、器件与夹具的反射、损耗与延时,SIM消除验证中的两大常见陷阱——失效误判(false failures)与能力误判(false confidence)——让结果反映你的器件而非搭建。

本文将探讨SIM如何为你提供对信号路径的完整可视性,从而为标准一致性与真实性能验证提供信心,加速产品上市。

通过去嵌入获得对DUT的准确可视性

在高速、RF与快速开关电力设计中,探头负载、电缆损耗与夹具反射很常见。如果不补偿这些非理想路径效应,你可能会误以为DUT有问题或不符合标准,而实际并非如此——导致失效误判。当无法直接探测,或标准要求在PCIe、USB、DDR等规定的标准化测试点(TP0、TP1、TP2等)观测时,去嵌入尤为关键。在这些情况下,去嵌入允许你将测量参考平面虚拟移动到所需位置。

使用SIM软件,你可以定义多种模型——S参数、传输线、RLC、传递函数、FIR、并联(shunt)——以校正搭建引入的损耗、反射与延时。SIM也支持级联多个模型来表示整个测量路径,让你完整观察DUT的真实信号行为。

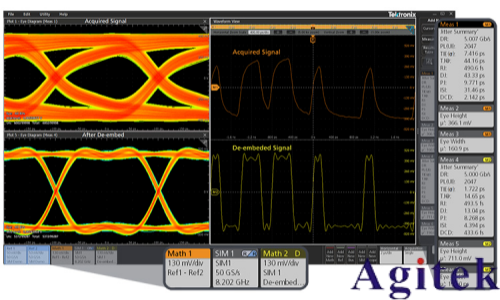

图1. 去嵌入前后:在 “SIM 1” 中定义的仿真输出至 “Math 2”,其中已去除测量伪影,得到更干净的波形与眼图。

通过嵌入来仿真真实世界效应

初期“干净”的测量可能带来能力误判——器件看似良好,但在真实系统中性能崩溃。阻抗不连续、通道损耗、反射与ISI都可能导致链路失效。嵌入也可能用于让DUT处于标准所需的负载阻抗之中。因此,嵌入真实世界效应对于一致性验证与部署前的系统级测试至关重要。

SIM允许你在示波器上虚拟嵌入真实互连——如背板、电缆或通道。举例而言,在USB3.0一致性测试中,SIM可嵌入PHY与控制器接口以确保其符合USB3.0标准。

你还可以直接在示波器上应用S参数模型来仿真各种环境,实现裕量分析与信号完整性验证,而无需构建或更换物理硬件。

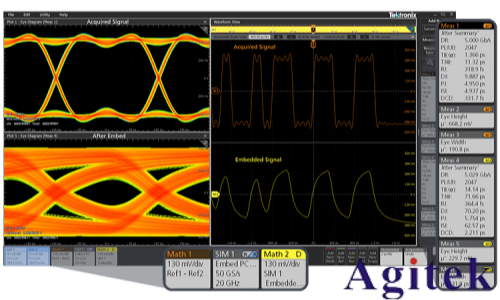

图2. 由于嵌入引入的ISI,眼高与眼宽降低。

用均衡打开闭合的眼图并验证性能

在当今数据速率下,通道会引入损耗、反射与串扰,从而压缩眼图,使定时与幅度裕量难以测量。均衡通过抵消失真、仿真真实接收机或发射机的处理方式来恢复可视性。结果是更干净的眼图、更准确的抖动/噪声测量,并增强系统达标的信心。

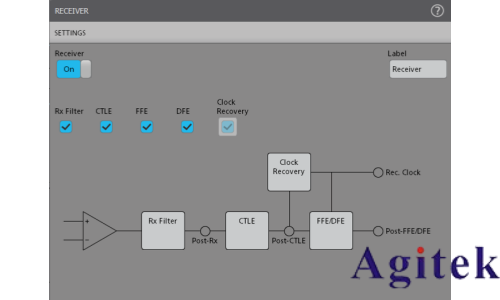

与以固定方式去除夹具效应的去嵌入不同,均衡是自适应的,会随频率相关行为与通道条件变化进行调整,让你看到接收机硬件中实际恢复的性能。发射端可用预加重/去加重做预处理;接收端可用CTLE、FFE、DFE来重建远端眼图。这些动态过程对PCIe、DDR5、USB3.0与多通道以太网等标准至关重要。

图3. SIM软件中的接收端均衡菜单。

SIM Advanced将这些能力集成到示波器中,让你无需直接接触芯片即可应用发射机EQ、构建自定义接收机模型并探索系统裕量。无论你的目标是一致性、调试还是设计探索,均衡都能让测量反映真实世界中的信号行为。

SIM Advanced(选件SIMA)计划于2026年初发布。

快速、易用且灵活

无论你专注于早期bring-up、一致性或调试,SIM的现代、直观UI都能让流程更简单。触控优化与清晰的界面使你无需成为专家即可上手。简化的工作流与现代化架构,可快速设置并处理从最简单到最复杂的去嵌入/嵌入滤波。

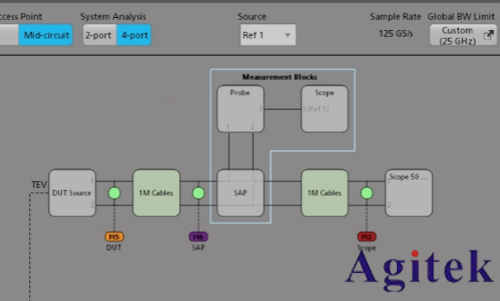

图4. 在 SIM菜单中的一个简单去嵌入示例:在M2测试点上,去嵌入所定义的物理模型后,得到 Math2波形。

强大能力:几乎不限数量的仿真与测试点

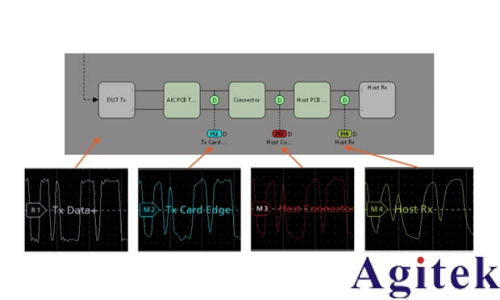

图5. 使用SIM对信号路径进行全面可视化。

SIM让你可以运行几乎无限数量的仿真与测试点。你可以在任意虚拟测量/测试点观察信号,查看每个模块前后的变化;也可对并行路径或更复杂的信号链建模,而不局限于一次只做一个仿真。结果以并排方式保留,便于直接对比原始与修正后的信号,并快速探索“假设”场景。

例如,你可以:

■ 在PCIe Gen4链路上评估不同CTLE/FFE设置,选择最能恢复眼裕量的组合;

■ 在DDR5调试中,在定版前比较多种夹具板/DIMM 连接器组合;

■ 在USB4/DisplayPort测试中,评估不同的线缆长度或过孔方案,而无需从头跑一遍流程。

在这些场景中,SIM将从反复返工的数小时缩短为几分钟的并行洞察。

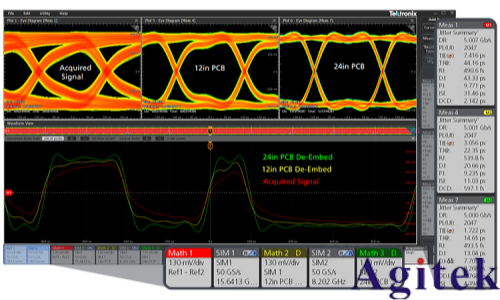

图6. 并行SIM可快速进行“假设”验证。例如,先去嵌入12英寸PCB走线,再用第二个模型去嵌入24英寸走线,以评估**设计性能与裕量。图中展示原始与去嵌入后的眼图/波形。

从更清晰的眼图到更深入的洞察:SIM搭配DJA

将SIM与Tektronix Advanced Jitter Analysis(选件 DJA)搭配使用,可更深入理解高速系统的传输质量。DJA可通过TIE、眼图、BER浴盆曲线与频谱分析分离抖动来源,并将总抖动分解为随机抖动(RJ)、确定性抖动(DJ)及其子项。基于这些洞察,你可以将抖动与潜在根因关联起来,并用SIM去嵌入、打开眼图。

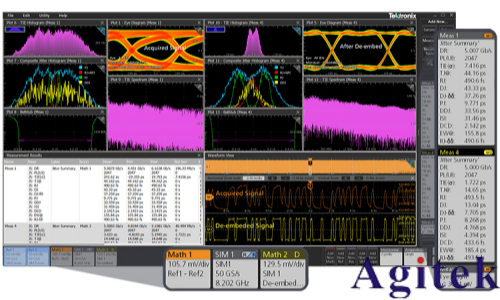

图7. 将获取与去嵌入后的信号进行对比:SIM与DJA联合分析(选件DJA)。

上图展示了SIM与DJA如何相互配合,揭示信号质量在物理与统计层面的改善。左上窗格显示采集波形,右侧窗格显示SIM去嵌入后的同一波形(去除了夹具与互连效应)。可以看到眼图显著打开,TIE直方图在时间轴方向变窄,表明总抖动减小、定时稳定性提升。

这也表明:虽然ISI与数据相关抖动(DDJ)已主要被去嵌入消除,但剩余抖动更多受周期性、确定性(相关)成分主导——可能来自发射端PLL相位噪声、电源耦合或低速时钟调制。结合TIE频谱(噪声底降低、随频率下倾)可见高频噪声被抑制、低频周期性漂移占主导。

浴盆曲线进一步确认了改善:曲线变宽且边缘更陡,说明误码概率降低、定时裕量扩大。SIM澄清了物理信号路径,DJA则量化了抖动演化,为工程师提供完整的一体化信号完整性与根因视图。

技术支持

关注官方微信

关注官方微信