基于普源数字示波器的AEC延迟与相位偏移测试方案

随着生成式AI(AIGC)和大模型的爆发式增长,算力集群对内部互连带宽的需求已从400G加速迈向800G乃至1.6T时代。在单通道112G PAM4的高速率下,传统无源铜缆(DAC)受限于趋肤效应与介质损耗,传输距离被物理锁定在2米以内,难以满足跨机柜互连需求。

AEC(Active Electrical Cable,有源电缆) 通过内置Retimer芯片进行信号均衡与放大,打破了铜缆的物理极限,成为实现3-7米低功耗、低成本互连的关键技术。然而,有源器件的引入也带来了新的测试挑战——特别是信号传输延迟(Latency)与通道间时延偏斜(Skew)的精确测量。本文将探讨如何利用高性能示波器应对这一挑战。

AEC测试的核心挑战:有源器件引入的时序不确定性

与无源线缆不同,AEC内部集成了CDR(时钟数据恢复)和均衡电路。这些有源器件在处理信号时会引入固有的传输延迟。

在高速并行传输系统中(如800G OSFP/QSFP-DD接口),多路信号必须保持极高的同步性。如果通道间时延偏斜(Skew)超过系统容限,将导致接收端无法正确恢复数据,进而引发链路CRC错误甚至Link Down。

因此,在AEC的研发与量产测试中,除了常规的S参数与误码率测试外,纳秒(ns)乃至皮秒(ps)级的延迟与相位一致性测量,是判定产品合格与否的关键指标。

高速有源线缆AEC

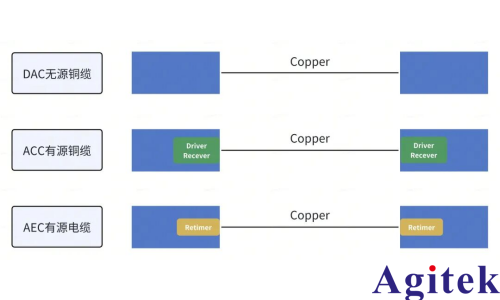

DAC,ACC和AEC在线缆结构上的区别

基于RIGOL DS9404数字示波器的测试系统构建

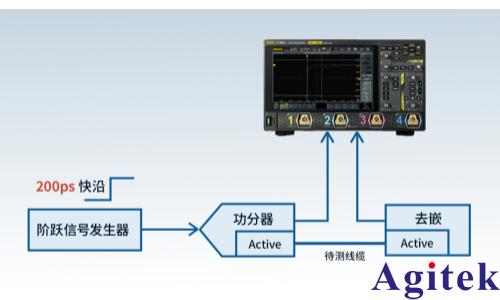

本方案采用参考路径与DUT路径的时域对比测量(TDR/TDT思路),通过两路同步采集计算Δt。

高精度激励源

使用一台能够产生快速上升沿(Rise Time < 200ps)的阶跃信号发生器作为基准源。

信号分配

利用高频功分器将基准信号一分为二:

参考路(Reference): 直接输入示波器通道,建立时序零点。

待测路(DUT): 信号穿过AEC线缆后输入示波器,作为被测信号。

精密测量

利用示波器同时捕获两路信号的阶跃边沿,通过测量参考信号与DUT输出信号之间的时间差Δt,直接获得线缆的传输延迟。

高速有源线缆AEC测试拓扑图

关键测量能力分析

在该测试方案中,示波器的性能直接决定了测量的准确度与重复性。RIGOL DS9404数字示波器凭借以下核心优势,成为AEC测试的理想选择:

高带宽和采样率

带宽可达4 GHz,采样率最高20 GSa/s,能够捕获高速信号且细节清晰。凭借着高带宽和高采样率可精确捕获高速脉冲信号的上升沿和微弱变化。

精确时延测量

可使用自动测量Delay(在固定阈值如50%处)、统计(均值/标准差)与直方图功能评估时延与重复性;结合通道Deskew提升通道间测量一致性。

长时间稳定测试

DS9404数字示波器支持高效的可编程控制(SCPI指令集)。在量产测试中,可配合自动化软件快速完成多通道的时延扫描与Pass/Fail判定,显著提升产线吞吐率(UPH)。

紧凑的体积

DS9404数字示波器突破传统4 GHz示波器的体积限制,采用高集成度的工业设计方案。其紧凑的机身可无缝嵌入标准机柜或狭窄的产线测试工位,显著优化空间利用率,有效缓解复杂测试环境下的设备堆叠与拥挤问题。

在AI算力基础设施的建设浪潮中,互连技术的可靠性至关重要。AEC作为连接算力节点的“大动脉”,其时序一致性是保证集群性能的基础。

RIGOL DS9404数字示波器,以其卓越的时域分析能力、高带宽与高采样率特性,为AEC的有源延迟与相位偏移测试提供了一套精准、高效且极具性价比的解决方案,助力下一代高速互连产品的质量验证与交付。

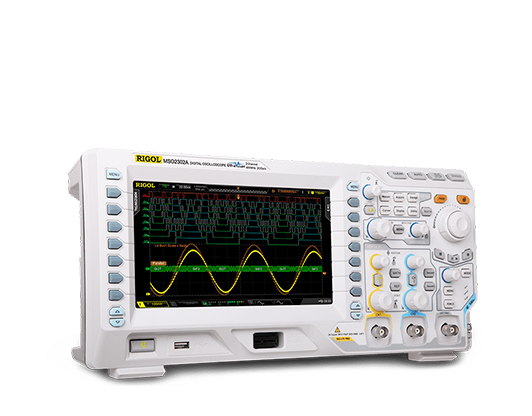

DS9404数字示波器

产品特点:

■ 模拟带宽 4 GHz

■ 最高实时采样率 20 GSa/s

■ 最大存储深度 2 Gpts(opt.)

■ 最高波形捕获率1,000,000 wfms/s

■ 模拟通道数 4

一直以来,普源精电专注于电子设计、测试、生产、优化,提供为满足客户需求的广泛解决方案及产品组合,并通过强化在硬件、算法及软件方面的技术实力,紧密对接客户需求和市场动态,持续探索提升产品应用的行业覆盖性。

技术支持

关注官方微信

关注官方微信