协议分析仪:洞悉 PCIe 通道的好帮手

当 AI 数据中心的算力需求呈指数级爆发,PCIe® 6.0 已然成为那条不可或缺的“高速公路”。但你是否想过,当双向带宽狂飙至 512 GB/s(PCIe® 7.0 规范),信号传输的每一个微小抖动都可能引发风暴?速度的跃升带来了前所未有的测试复杂度,工程师们急需一双能够“透视”高速通道的眼睛。今天,我们就来聊聊这双“火眼金睛”——PCIe 协议分析仪,看它如何在不降低信号完整性的前提下,帮你洞悉数据传输的每一个细节。

本文将系统介绍 PCIe 协议测试的基础知识、协议分析仪的核心功能与工作原理,并探讨其如何助力解决 PCIe 验证过程中的技术挑战。

什么是协议分析仪?

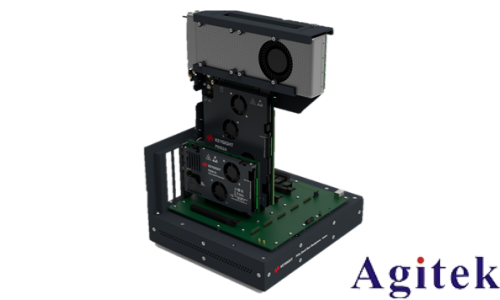

图1:是德科技P5570A PCIe 6.0 协议分析仪,P5573A PCIe 6.0 训练器,两者均固定在底部的测试背板上

在电子测量领域,PCIe协议分析仪的作用是捕获并解析PCIe总线上的数据包,用于性能评估、故障排查、兼容性测试和系统优化,是开发、调试和验证PCIe设备不可或缺的工具。它用极高信号保真度的interposer 把PCIe链路上的所有协议流量捕获下来,通过同时洞察 PHY/DLLP/TLP 三层的行为,分析仪可以完整监控整个系统在训练、数据交换与错误恢复过程中的真实运行状态。

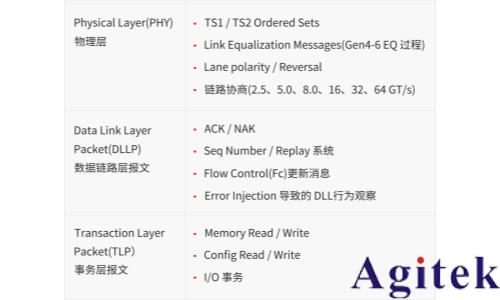

表1:PCIe总线数据包主要内容

对于工程师而言,理想的协议分析仪需要具备完全透明性,这样它就不会因其自身电路或电缆引入额外的信号完整性误差,也不会影响任何通信系统的功能。此外,它还应具有极低的延迟并且几乎没有性能损耗。工程师可以选择使用专用的硬件仪器、通用仪器的内置软件功能,或者离线分析软件。每种方式都有其各自的优缺点,如下所述:

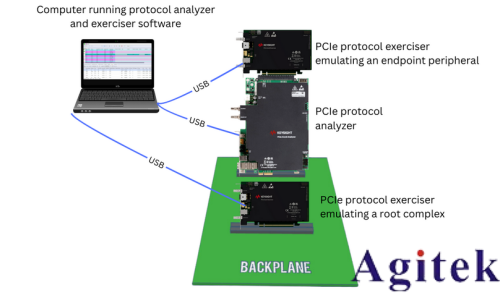

图2:专用 PCIe 协议分析仪与训练器硬件

专用协议分析仪与训练器硬件能提供最严格、最深入的测试与分析能力。例如,在上图所示场景中,是德科技P5570A PCIe 6.0 协议分析仪这类专用 PCIe 协议分析硬件,可捕获根复合体(Root Complex)与外围设备之间的 PCIe 通信数据,且不会引入任何干扰或信号完整性误差。它会将捕获到的数据实时传输至另一台计算机进行分析和可视化处理。借助是德科技PCle 6.0 协议分析仪(P5570A)及训练器(P5573A)这类专用协议硬件,可对根复合体、外围设备,或两者同时进行严格且精准的仿真。这种专用硬件仪器组合,能够对相关场景及边界情况进行全面的功能与性能测试。

示波器等通用仪器也具备协议解码功能。不过,这类功能虽便于快速进行功能检查,却可能不具备专用硬件所拥有的深入、全面的分析能力。例如,是德科技InfiniiVision 系列示波器可捕获车载网络协议,其设备内置的软件组件能将捕获到的比特流解码为特定协议的指令与数据,并直接显示在仪器屏幕上。是德科技 Infiniium UXR 系列示波器也有针对 PCIe 及其他高速数字标准的类似协议解码软件。

协议分析仪适用的场景

PCIe 协议分析仪与训练器可支持对多种设备拓扑结构的测试,以下是常见的测试应用场景:

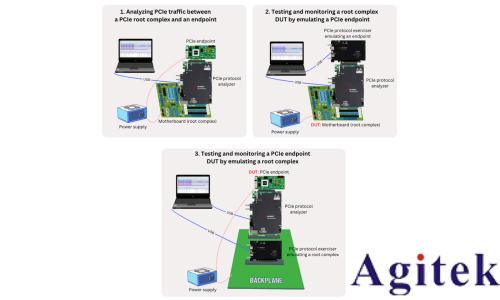

图3:适用于不同使用场景的 PCIe 协议分析仪与训练器配置示意图

分析根复合体与端点设备间的 PCIe 通信:将分析仪部署在物理根复合体(Root Complex)与 PCIe 端点设备(Endpoint Device)之间,测试二者的互操作性。

仿真根复合体以测试端点设备:由训练器仿真根复合体,将其与协议分析仪连接,分析仪再与被测件相连。这种配置可帮助设备制造商进行 PCIe 一致性测试。

仿真端点设备以测试根复合体(RC):由训练器仿真各类端点设备,并与分析仪连接;待测试根复合体则连接至分析仪的另一端。通过这种方式,可让根复合体接收来自不同设备的多种 PCIe 通信信号,从而完成对根复合体的测试。

PCIe 协议测试面临哪些挑战?

在下一代 AI 数据中心中测试 PCIe 协议,主要面临 三大关键挑战。

01在不丢失数据情况下捕获高数据速率

PCIe 6.0 的高速数据传输(双向速率均高达 256 GB/s)对测试仪器提出了高要求,需要借助高速仪器实现无丢失的数据捕获。

02保持信号完整性且不受干扰

高速数据传输会导致信号反射与串扰,因此,防止信号劣化和通道损伤至关重要,但与此同时,协议分析仪在测试系统中需实现“无存在感”工作:既不能无意中改善已存在的信号劣化问题,也不能对时序误差进行修正(需如实反映原始信号状态,以确保测试结果准确)。

03可视化复杂的协议事务

每一代 PCIe 规范都会引入更复杂的事务处理机制,因此必须具备先进的解码与分析能力,才能跟上协议复杂度的升级步伐。

协议分析仪如何工作?

01. PCIe 协议分析仪如何解码并呈现捕获的流量?

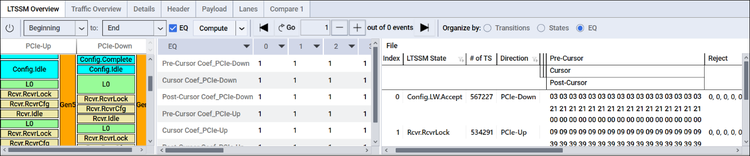

为进行有效调试与故障排除,是德科技P5570A 协议分析仪及其配套的 P5500 软件,会通过友好的图形用户界面(GUI)呈现所有协议层的详细信息。底层链路初始化是关键流程,也是诸多错误的源头。如下所示,通过LTSSM 视图查看状态变化,设备底层运行情况一目了然。

图4:LTSSM 视图

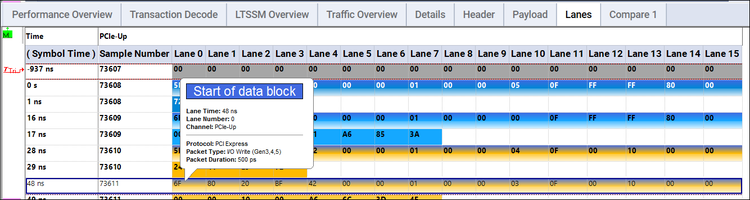

链路建立后,通道视图(Lane View)可深入呈现底层数据传输情况——如图所示,该视图能显示每条 PCIe 通道(Lane)中正在传输的精确符号(Symbol)及其对应的两位序列(Two-bit sequences),帮助工程师直观观察物理层的信号传输细节(如符号完整性、传输顺序)。

图5:通道视图

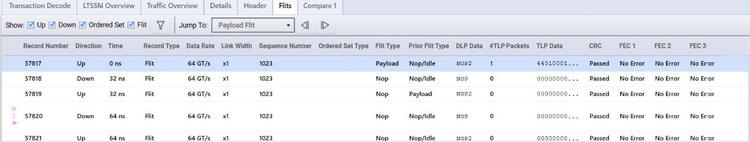

FLIT发送是否正常?FEC与循环冗余校验(CRC)功能是否无误?这些问题可以通过查看如下的 FLIT 视图来解答——该视图可清晰展示 FLIT 的结构(头部、数据、尾部)、嵌入的 FEC 编码与 CRC 编码,以及相关校验结果,帮助工程师快速判断数据在物理层传输中的完整性与纠错机制有效性。

图6:FLIT 视图

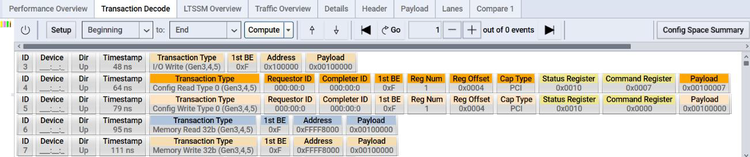

高层事务(High-level Transactions)可通过事务解码界面(Transaction Decode Screen)进行分析——该界面会将物理层传输的原始数据解码为事务层可识别的事务层数据包(TLP),清晰展示读/写操作的地址、数据长度、事务类型及状态等关键信息,助力工程师排查事务层的协议交互问题(如异常 TLP 格式、事务响应超时等)。

图7:事务解码界面

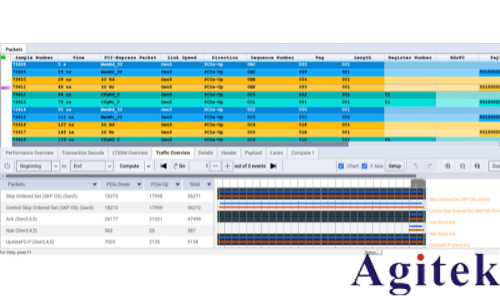

事务相关的TLP与DLLP可在如下所示的数据包视图(Packet View)与流量概览界面(Traffic Overview Screen)中查看:

数据包视图:会逐一展示每个 TLP 和 DLLP 的完整结构(如头部字段、有效载荷、校验码),便于工程师核查单个数据包是否符合 PCIe 协议规范;

流量概览界面:则以宏观视角呈现一段时间内的 TLP、DLLP 传输总量、速率及错误包占比,帮助快速定位流量异常(如突发丢包、错误包激增)的时间节点。

图8:数据包与流量概览界面

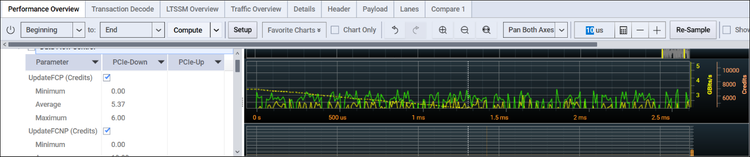

PCIe 性能测试与功能验证同样关键。如图所示,性能视图(Performance View)会展示关键的时序与速率指标(如事务响应延迟、每通道实际传输速率、带宽利用率等),帮助工程师精准识别性能瓶颈(例如,响应延迟过长导致的传输卡顿、带宽未达设计值等问题)。

图9:性能概述

02. PCIe 协议分析仪如何处理前向纠错(FEC)?

P5570A 和 P5573A 这样的协议分析仪与训练器在设计时采用了以下策略,确保不会对前向纠错(FEC)机制的功能或性能产生影响:

非侵入式设计:该设备完全不会修改或干扰FEC过程。其设计旨在确保对PCIe链路实现完全透明(即链路无法感知分析仪的存在,不影响链路正常交互)。

低延迟拦截:为满足 PCIe 性能标准,FEC延迟必须低于 2 ns。协议分析仪的设计符合这些严苛的延迟要求,确保工程师能够准确掌握链路真实的性能表现。

支持流量控制与信号传输技术升级:协议分析仪与训练器的设计可适配 PCIe 6.0 的技术改进,如固定大小的 FLITs 帧与 PAM4 信号调制,这些改进对于FEC过程至关重要。

纠错效果监测:P5570A 等高端协议分析仪能够监测 FEC 的有效性,可分析 FEC 各步骤的状态,并核查 FEC 纠错是否成功、循环冗余校验(CRC)是否通过。

全面测试自动化:要有效验证 FEC 性能,需借助完善的测试自动化功能开展压力测试与仿真 —— 在各类场景下对 FEC 进行测试。这包括通过应用程序接口(API)刻意改变信号条件、注入错误,以此评估 FEC 的抗干扰能力(稳健性)。

是德科技PCIe协议分析仪解决方案

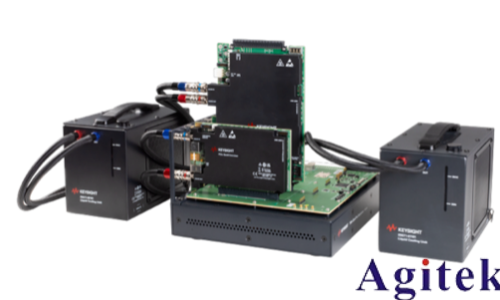

图10:PCIe 5.0协议分析仪及训练器(左)PCIe 6.0协议分析仪及训练器(右)

是德科技的PCIe5.0/6.0协议分析仪和训练器采用了创新的CEM卡外形设计,将分析仪和内插器(Interposer)整合在一起,可以凭借其高信号完整性能为 PCIe 设备提供最精准的数据分析。工程师们从而可以专注于设备本身的调试工作,无需担忧测试仪器是否引入新问题或覆盖已有问题。

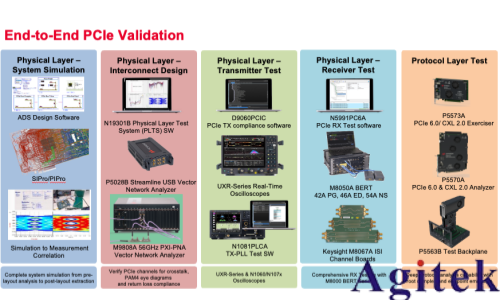

图11:PCIe 6.0端到端解决方案

是德科技一直致力于突破性测量技术的研发,不断突破高速数字技术的创新边界。下一代PCIe 7.0®互连技术,将使每个引脚的数据传输速度提高到 128 GT/s ——双向传输带宽将高达512 GB/s。PCIe 7.0®性能翻倍的背后,是工程复杂度与部署挑战的直线上升,从信号完整性、电路板设计,到系统散热与能耗控制等各个方面对系统平台提出了更严苛的要求。是德科技提供从设计仿真到物理层收发端以及协议分析测试一站式解决方案,助力屏幕前的你们成功解决PCIe技术难题。

技术支持

关注官方微信

关注官方微信