DDR5技术演进与全链路测试解决方案深度解析

在数字化浪潮推动下,存储器件已成为支撑现代电子系统的核心基础设施。作为当前主流的内存技术,DDR SDRAM(双倍数据率同步动态随机存取存储器)历经五代技术迭代,其传输速率已突破6.4Gbps大关,同时功耗较前代降低20%以上。这种指数级性能跃升背后,是信号完整性、时序精度和系统协同等测试维度的几何级复杂度增长。本文将系统解析DDR5技术特性,并阐述其全链路测试解决方案。

一、DDR5技术架构革新

DDR5标准在继承前代技术精髓的基础上,实现了三大维度突破:

性能维度:数据速率从DDR4的3200MT/s提升至6400MT/s,通过16n预取架构将突发长度扩展至BL16,使内存带宽密度实现翻倍增长。

能效维度:工作电压从1.2V降至1.1V,配合PMIC电源管理芯片实现动态电压调节,单位比特能耗降低达30%。

密度维度:单颗粒容量突破64Gb,通过32Bank Group架构设计显著提升并行访问效率,特别适用于AI训练等高并发场景。

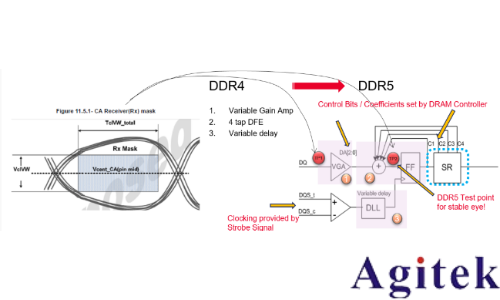

技术演进背后是底层架构的颠覆性创新:DDR5首次引入SerDes技术,采用DFE(决策反馈均衡)和CTLE(连续时间线性均衡)混合均衡方案,有效解决了高速信号传输中的ISI(码间干扰)问题。同时,CA总线训练机制的引入,使时序参数从固定阈值转向动态适配,这对测试系统的实时分析能力提出全新要求。

二、DDR5测试技术挑战

面对6.4Gbps的信号速率,传统测试方法遭遇三大瓶颈:

信号完整性分析:眼图闭合程度加剧,要求测试设备具备≥50GHz带宽和10bit垂直分辨率

抖动分解精度:需区分RJ(随机抖动)、DJ(确定性抖动)等12类抖动成分,测量不确定度需控制在0.1ps以内

协议解码深度:需实时捕获200层以上协议栈交互,支持PRBS31伪随机序列的误码率测试

三、全链路测试解决方案

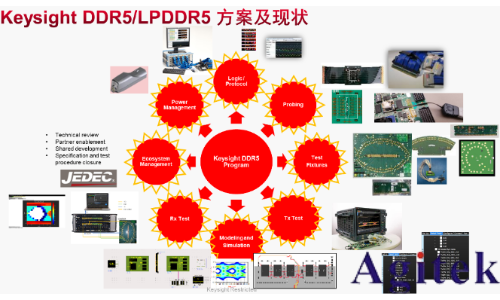

作为JEDEC标准制定核心成员,是德科技构建了覆盖物理层到协议层的完整测试体系:

1. 发射端测试方案

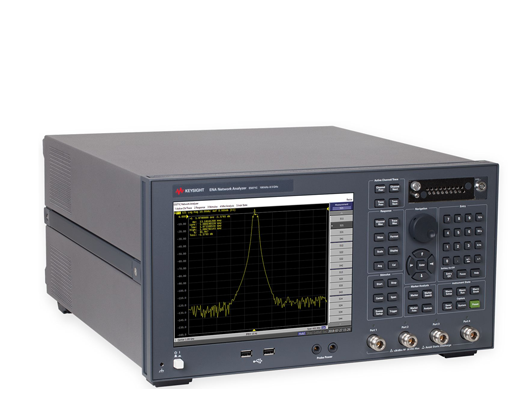

采用UXR系列110GHz实时示波器,配合D9050DDRC自动测试软件,可实现:

12类眼图参数自动测量(Eye Height/Width/Mask等)

抖动成分分解(RJ/DJ/PJ/BUJ等)

预加重/去加重效果验证

S-参数模型提取与信道仿真

2. 接收端测试方案

基于M8020A 32Gbps误码仪和UXR示波器,构建闭环测试系统:

支持DQS/DQ/CA总线灵敏度测试

DFE均衡器特性表征(Tap系数优化)

应力眼图测试(Stressed Eye)

电压/时序容限分析(Voltage/Timing Margin)

3. 协议层测试方案

U4164A逻辑分析仪搭载B4661A存储器分析软件,提供:

实时协议解码(支持DDR5所有命令集)

200层以上协议栈追踪

时序违规定位(Setup/Hold Time Violation)

功耗分布分析(Power Consumption Profiling)

4. 系统级测试方案

针对RDIMM/LRDIMM模块,提供:

FS2600 Interposer夹具实现信号无损采集

W5643A BGA Interposer支持芯片级测试

电源完整性分析(PDN Impedance Measurement)

热仿真与可靠性验证

四、技术演进展望

随着PCIe 6.0和CXL 3.0等高速协议的普及,DDR内存测试正朝着"三超"方向发展:超高速率(12.8Gbps+)、超低抖动(<50fs RMS)、超宽频带(100GHz+)。是德科技最新推出的UXR0504A示波器,凭借110GHz带宽和256GSa/s采样率,为DDR6时代测试做好了技术储备。

在AI算力爆炸式增长的背景下,DDR内存测试已从单一参数验证转向系统级性能评估。通过构建涵盖设计仿真、信号采集、协议分析和系统验证的全链路测试平台,工程师能够更高效地平衡性能、功耗和成本三大约束,加速下一代存储产品的上市进程。

技术支持

关注官方微信

关注官方微信