RISC-V芯片:如何打造仿真到测试的完整验证闭环

RISC-V 的发展背景与全球趋势

RISC-V 作为新一代开放指令集架构(ISA),已经从学术界的概念研究快速走向全球产业化浪潮。在短短数年内,它从“开源替代方案”成长为全球半导体生态的重要力量,成为 CPU 架构演进中最具活力的选项之一。

全球崛起:从开源实验室到产业级生态

RISC-V 的核心优势来自其 开源、免费、可扩展、可裁剪 的本质,使其迅速获得产业界认可。

RISC-V International(原RISC-V基金会)目前覆盖 70 多个国家、超过 4000 名成员

生态成员包括:谷歌、英伟达、IBM、Qualcomm、阿里巴巴、三星、西部数据(WD)等全球科技巨头,同时也吸引了大量初创企业与科研团队加入。

市场规模爆发:进入数十亿级别的商业时代

过去十年中,RISC-V 从“验证阶段”进入“规模商用阶段”,出货量呈指数增长。

全球市场预测

2025 年全球 RISC-V 芯片出货量预计突破 20 亿颗。2030 年有望达到数百亿片规模,成为全球增长速度最快的 CPU 架构之一。其中约 50% 的增长来自中国,包括 AIoT、智能终端、边缘计算、车规 MCU 等广泛场景。

AI 加速赛道成为增长引擎

面向推理、训练、AI 算子加速的 RISC-V AI SoC 有望在未来 5–7 年内达到数十亿颗级别的市场规模。由于 RISC-V 可让企业自由扩展自定义指令(如矩阵运算、向量引擎等),非常适合构建 轻量级、高能效比的 AI 加速芯片。

技术竞争格局:向 “X86 + Arm + RISC-V” 三足鼎立演变

RISC-V 的开放性和可扩展性正在改变传统 CPU 的竞争逻辑。全球 CPU 架构正步入新的竞争平衡点。随着 RISC-V 的生态加速完善、工具链不断成熟、商业化案例逐年增多,行业开始出现明确趋势:CPU 架构体系正从“两极格局”走向“X86 + Arm + RISC-V”三足鼎立的新阶段。

RISC-V 时代的验证挑战

从测试的角度看,RISC-V 与 x86 / Arm 的验证本质上并无“架构本身决定的难点差异”, 真正的差别在于:RISC-V 的灵活性远高于传统架构,但行业尚缺乏成熟的工具链、案例和 SOP,因此“验证经验不够沉淀”。

因此,RISC-V 测试中普遍会遇到三个现实挑战:

(1)缺少可复用的验证流程

不同公司、不同项目、不同自定义 ISA 都有自己的验证方法,没有形成像 Arm/x86 那样的标准化路径。

(2)缺少全过程的一致性测试验证

EDA 仿真一套语言,硅测一套语言,系统调试又是一套,结果常常无法连贯,一致性缺失。

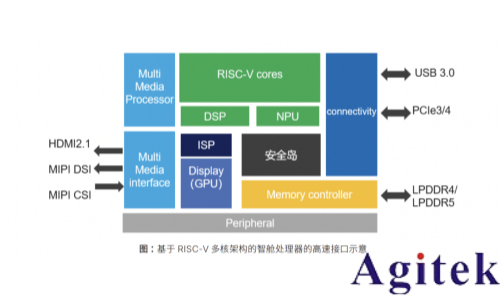

(3)缺少成熟的高速接口调试经验

当 RISC-V 芯片开始进入 AI、汽车、数据中心等高端场景,高速接口(PCIe、DDR、CXL、Ethernet)成为真正的痛点来源。

综上所述,RISC-V 的验证难点不在于“架构难”,而在于生态仍缺乏一条真正完整、协同、连贯的 End-to-End 验证链路——从前仿真,到半实物平台,再到硅测与系统级验证。

是德科技的完整验证方案

(从ADS仿真到后硅测试)

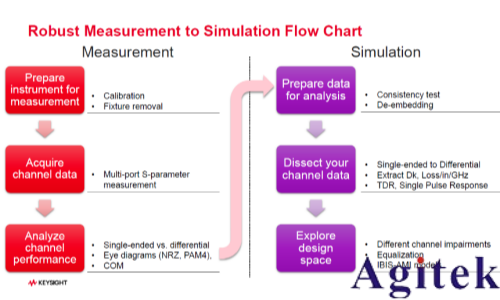

面对RISC-V芯片设计和验证的多重挑战,是德科技(Keysight)则是从仿真、半实物仿真、无源测试验证、有源测试、功能和系统测试,以及用相同的算法拉通全过程来加速这一过程。其核心理念是在产品开发全流程中形成“闭环”验证链路解决方案。下图是PCB/Cable/Fixture设计和验证的仿测闭环流程实例。

图:是德科技的PLTS物理层测试方案和ADS仿真软件形成仿测闭环验证

在设计阶段,是德科技的ADS (Advanced Design System) 等EDA仿真工具发挥关键作用。工程师可以利用ADS对高速接口电信道进行信号完整性(SI)仿真、对电源分配网络进行电源完整性(PI)分析。例如,通过ADS的PIPro模块可以仿真芯片/板级电源网络的IR压降和阻抗分布,预测不同去耦方案对电压纹波的影响。对于PCIe、DDR、以太网等高速链路,则可在ADS中建立拓扑模型,进行时域与频域仿真,评估插损、抖动、眼图裕量是否满足标准要求。这些仿真能够在设计初期阶段发现潜在信号/电源问题,指导硬件布局布线和IP参数选型,避免走线不良或电源噪声过大导致后期整改。

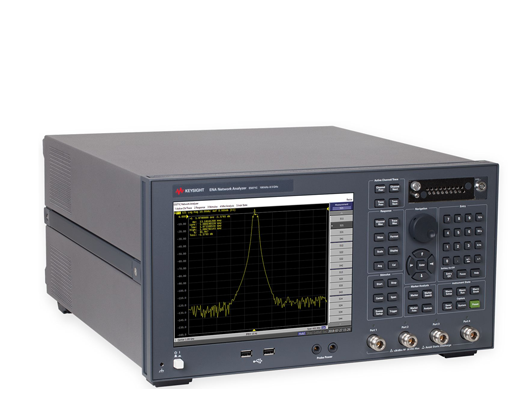

进入产品实现阶段后,是德科技提供一系列尖端测试测量设备,帮助工程师验证实际芯片和系统与仿真预期一致,完成最终的硅后验证。例如,使用超高带宽实时示波器(如Keysight UXR系列)测量高速接口的发射信号眼图和抖动,对比仿真得到的眼图指标,验证设计裕量;利用矢量网络分析仪(VNA)对封装、PCB走线和连接器的S参数进行测量,并通过去嵌技术除去治具影响,将实测信道特性与ADS仿真模型对应比对,从而校准模型精度。同时,是德科技的测试方案注重自动化和相关性:许多仪器配套软件可自动执行标准一致性测试,用脚本一次性跑完整套用例并生成报告;仿真结果和测量数据可以在同一平台下关联分析,帮助快速定位差异原因,实现设计与测试的无缝衔接。

通过将前端设计仿真与后端硬件测试紧密耦合,是德科技构建了一个覆盖RISC-V芯片全生命周期的验证闭环。这种方案能够在实验室里重现复杂的场景,提早暴露问题并指导设计改进,避免流片后才发现纰漏而被迫修复。事实证明,借助仿真-实测闭环,可以显著降低开发风险和成本——例如在高速接口设计中,仿真阶段锁定优化参数可减少一次PCB迭代。凭借深厚的技术积累,是德科技构筑的这一完整验证链路,为RISC-V芯片从概念到落地保驾护航,帮助工程师大幅提升验证信心和效率。

对于芯粒测试,ADS仿真、去嵌、和物理层测试方案的结合显得更加必要,下图是芯粒测试的流程实例。

图:芯粒测试的流程

PCIe、DDR、CXL、Ethernet、

电源/信号完整性测试场景概览

RISC-V芯片要在各种应用中可靠运行,离不开对其高速接口和板级性能的严格测试。是德科技的方案广泛覆盖了主流接口标准和完整性验证需求,典型场景包括:

PCI Express (PCIe):无论是在数据中心将RISC-V处理器与GPU加速卡相连,还是在嵌入式设备中扩展高速外设,总线接口PCIe都是关键纽带。是德科技提供从PCIe 1.0到最新6.0的物理层和协议层一致性测试方案,可对发射端眼图和抖动、信道插损和回损、接收端误码率等进行全面测量。配套的协议分析仪和协议发生器则用于验证链路训练状态机(LTSSM)、错误处理等协议行为。借助如UXR系列示波器、M8000A系列误码仪、PNA/PNA-X/PNA-L矢量网络分析仪及P5570A 和 P5573A PCIe 6.0 协议分析仪测试工具,工程师能够高效完成PCIe链路的一致性认证和调试,确保RISC-V芯片与现有PCIe生态无缝互通。

DDR内存接口:RISC-V处理器广泛用于高性能计算和AI加速时,常需连接高速DDR/LPDDR内存。是德科技的解决方案覆盖DDR3/4/5及LPDDR5/6等标准,从时钟抖动、信号眼图、命令总线时序到电压噪声均有针对性的测试项目。通过高带宽示波器配合DDR一致性测试软件,可自动化测量读写眼高/眼宽、时序参数(tDQSQ、tDQSCK等)是否达标;结合误码仪可以模拟加扰噪声验证数据可靠性。此外,是德科技还提供前仿真到后测量的一体化DDR分析工具:IBIS模型仿真布线拓扑,实测S参数比对仿真眼图,帮助客户在DDR接口设计中实现仿真-测试闭环,平滑升级到新一代存储器。

CXL高速互连:Compute Express Link (CXL)是新兴的基于PCIe的缓存一致性互连,总线标准复杂且要求严格。针对采用CXL架构的RISC-V 芯片,是德科技的PCIe5.0/6.0测试平台同样适用:能够测量CXL链路的物理层信号质量,并通过协议分析仪验证CXL的一致性协议(如内存缓存一致性、设备内存映射)是否正确实现。利用Keysight提供的PCIe/CXL协议触发和解码工具,可以在链路训练、读写事务中捕获异常,确保RISC-V芯片在CXL互连下数据一致且延迟可控。

高速以太网 (Ethernet):许多RISC-V应用(例如网络处理器、物联网网关等)需要支持千兆乃至更高速率的以太网通信。是德科技具备从1GbE到400GbE/800GbE以太网物理层的一体化测试能力。通过误码仪和示波器相结合,可测试高速SERDES链路的误码率、抖动容限和眼图裕度;使用矢量网络分析仪能评估高速差分线路的特性阻抗匹配和模式转换。针对以太网标准,还支持自动一致性测试套件,覆盖IEEE规范要求的电气参数测试,帮助工程师快速判断设计是否符合Ethernet标准。无论是板上走线还是光模块接口,都可以在Keysight平台上完成全面的物理层验证,为RISC-V芯片的网络通信功能提供信心保障。

电源和信号完整性 (PI/SI):随着芯片工艺和速率的提升,板级电源稳定与信号质量对系统性能的影响愈发突出。是德科技将PI/SI测试纳入验证链路中,提供专门工具监控和优化这些“看不见”的细节。例如,通过高速示波器配合电源轨探头,可以测量芯片供电的瞬态纹波噪声,并使用专用分析软件评估电源噪声对高速数据眼图的影响。在信号完整性方面,利用矢量网络分析仪获取走线的S参数后,工程师可以在ADS里仿真不同补偿方案(如预加重、均衡),再将其应用于实际电路验证效果。此外,Keysight提供抖动/干扰注入工具,可在实验室重现极端干扰场景,检验RISC-V芯片的抗扰裕度。通过这一系列软硬件手段,电源和信号完整性问题能够在设计早期就被发现并解决,确保最终产品在苛刻环境下依然稳定工作。

综上,是德科技构建了覆盖PCIe 1.0~6.0、DDR3~5/LPDDR6、Ethernet 400G/800G等各类高速接口,以及板级SI/PI性能的完整测试方案,涵盖了从发送端、信道到接收端的全流程验证。通过模块化的软硬件组合,该方案几乎囊括了RISC-V芯片可能涉及的所有测试场景,真正做到一站式保障芯片各方面指标的符合性和可靠性。

结语:从开放指令集到验证闭环的落地路径

开放的RISC-V指令集正为计算产业带来创新活力,但要将这份潜力转化为可靠的产品,完善的验证闭环至关重要。针对RISC-V芯片设计弹性大、验证难度高的特点,是德科技以其专业测试测量能力打造了从仿真到测试的全覆盖解决方案,弥合了设计预期与实际性能之间的鸿沟。在这种闭环验证思路的护航下,RISC-V芯片的开发风险大大降低,创新者们可以更大胆地探索定制化设计而无后顾之忧。

展望未来,RISC-V就像给算力生态开辟了一个“新接口”:它既能与现有的GPU、PCIe、以太网等体系协同合作,又能玩出指令级和架构级定制的新花样。随着软硬件生态日趋成熟,有了从设计到测试的闭环保障,RISC-V的落地之路将更加稳健而快捷。或许再过几年,我们日常使用的手机、电脑、智能汽车中都将出现RISC-V芯片的身影。是德科技将持续深耕测试测量技术,携手产业伙伴完善这一开放架构的验证体系,加速迈向一个开放创新、闭环可靠的RISC-V新时代。

技术支持

关注官方微信

关注官方微信